News & Updates

An optoisolator is a cool electronic device that can be used to pass information between a diode without passing an electrical current. There are many great applications for these, but do you know which one is right for you?

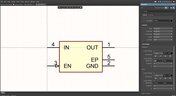

The Properties panel provides access to the properties of documents and objects. The contents of the panel change depending on the active document or the selected object. This blog will quickly go over some of need to know options around the properties panel in the schematic document.

Even with all the good guidelines out there for high speed design, there are particular aspects of stackup construction and their relation to building boards that get overlooked. This blog is goes beyond just the typical SI/PI guidelines and looks at these problems from more of an engineering perspective.

Stitching vias are something you often see spread around the surface layer of a PCB, but what are they? and should you be using them? In this guide, we'll go over some of the standard uses of stitching vias and when they should be used in a PCB.

In comparison to the build-up of a PCB, the stackup is more concerned with the electrical type of each layer, that is are we working with signals, power, or ground. Continue reading to learn how you can optimize your layer stack.

Altium’s VP of marketing Lawrence Romine discusses the multi-board and harness design capabilities coming in Altium Designer 23.

Controlled ESR capacitors are important for power integrity in your design as they can help smooth out the PDN impedance spectrum in your high speed PCB.

Take a look at the inside of some integrated circuit packages, and you’ll find a number of wires bonded to the semiconductor die and the pads at the edge of the component's package. As a signal traverses makes its way along an interconnect and into a destination circuit, signals need to travel across these bond wires and pads before they are interpreted as a logic state. As you look around the edge of an IC, these bond wires can have different lengths, and they incur different levels of delay and contribute to total jitter.

Once you’ve run out of room on your 4-layer PCB, it’s time to graduate to a 6-layer board. The additional layer can give you room for more signals, an additional plane pair, or a mix of conductors. How you use these extra layers is less important than how you arrange them in the PCB stackup, as well as how you route on a 6-layer PCB. If you’ve never used a 6-layer board before, or you’ve had EMI troubles with this stackup that are difficult to solve, keep reading to see some 6-layer PCB design guidelines and best practices.

We are happy to announce that the Altium Designer 22.5 update is now available. Altium Designer 22.5 continues to focus on improving the user experience, as well as performance and stability of the software, based on feedback from our users. Check out the key new features in the What's New section on the left side of this window!

PCB stackups often incorporate slightly dissimilar materials that could pose a reliability problem. Hybrid PCBs are one case where the PCB stackup will include different materials, typically a standard FR4 laminate and a PTFE laminate for RF PCBs. Designers who want to take the lead on material selection when designing their hybrid stackups should consider these factors that affect reliability. As with any PCB stackup, make sure you get your fabricator involved in the manufacturing process early to ensure reliability problems do not arise during production.

In a previous article about circuit simulation and reliability, I looked at how Monte Carlo analysis is commonly used to evaluate circuits that are subject to random variations in component values. Sensitivity analysis is a bit different and it tells you how the operating characteristics of your circuit change in a specific direction. Compared to a Monte Carlo simulation, sensitivity analysis gives you a convenient way to predict exactly how the operating characteristics will change if you were to deliberately increase or decrease the value of a component.

Field Programmable Gate Arrays, or FPGAs, have become ubiquitous amongst high-speed, real-time digital systems. The speed at which FPGAs operate continues to increase at a dizzying pace but their adoption into Continuous Integration pipelines seems not to trail as closely. In this article we will review the concept of CI pipelines, their application to FPGAs, and look at examples on how to set this up.

Conflicts can occur when multiple people work on the same project simultaneously. The user might not realize that they are not looking at the latest version of the documentation, leading to problems later. To address this issue, Altium features an intuitive graphical user interface that allows you to examine conflicts quickly and carefully

Anytime you place a component in your PCB, it’s almost like you’re gambling. All components have tolerances, and some of these are very precise, but others components can have very wide tolerances on their nominal values. In the event the tolerances on these components become too large, how can you predict how these tolerances will affect your circuits?

If you look in datasheets for most components, you’ll often find a recommended land pattern, usually alongside some mechanical package information and assembly information. This is not always the case with BGA components, especially components with high ball count. There are a few reasons for this that we can speculate: those ball counts might just be too big to put into a single page, or the manufacturer just expects you to know how to create that land pattern.

Molded interconnect devices are essentially plastic molded substrates with traces running along any surface, including at right angles and running vertically. Altium users can use the new 3D Routing extension to design their own component carriers, which can be mounted vertically in a standard assembly process. If you’ve always wanted to vertically mount components or entire circuits, but without the expense of adding a flex section to your design, the new 3D Routing extension with HARTING’s component carrier designs provides a unique solution.

Altium has released version 2.9.0 of the MCAD CoDesigner. This version has the option to exclude small components when transferring from ECAD to MCAD. The arc behavior was improved, and the support for splines in board shape and cutouts was added. With this release, you can now select a specific SOLIDWORKS configuration of a part to use on the board and view the improvements made for Siemens NX.

Altium Designer's world-class PCB design features help users quickly get started with new rigid-flex designs and prepare them for manufacturing. Rigid-flex in Altium Designer starts with designing a manufacturable PCB layer stack complete with via transitions and any calculated impedance requirements. Keep reading to see how Altium Designer supports your flex and rigid-flex designs.

Like any other advanced PCB, success in HDI design comes from designing the right stackup. One common HDI stackup used to support routing into moderate pin count, high-density BGA components is the 2+N+2 PCB layer stack for HDI boards. We’ll explore this stackup more in this article, as well as how it is related to other advanced stackups used in HDI PCBs.

Altium 365 Web Viewer now includes a built-in PDF viewer that allows you to view PDF files in releases without an external PDF viewer application. Keep reading to learn about new key features that make your work easier

There are two basic reasons for designing a flex circuit into your product: to build a compact and efficiently assembled device, or to make the circuit dynamically integrated with the mechanical function of the product. You may, of course, lean on both of these reasons for justifying the use of flex circuits. On this note, let’s look at some rigid-flex PCB applications and design examples to see the issues that spring to mind when designing flex circuits

With Altium 365, you can grant permission to teams or users based on the specific needs of a project. We have expanded Altium 365’s file-sharing setting, giving you more granular control over who can download source files and reshare projects with others