News & Updates

Designers often conflate leftover annular ring and pad sizes - they need to place a sufficiently large pad size on the surface layer to ensure that the annular ring that is leftover during fabrication will be large enough. As long as the annular ring is sufficiently large, the drill hit will not be considered defective and the board will have passed inspection. In this article, I'll discuss the limits on IPC-6012 Class 3 annular rings as these are a standard fabrication requirement for high-reliability rigid PCBs.

Sending a board out for fabrication is an exciting and nerve-wracking moment. Why not just give your fabricator your design files and let them figure it out? There are a few reasons for this, but it means the responsibility comes back to you as the designer to produce manufacturing files and documentation for your PCB. It’s actually quite simple if you have the right design tools. We’ll look at how you can do this inside your PCB layout and how this will help you quickly generate data for your manufacturer.

As the world of technology has evolved, so has the need to pack more capabilities into smaller packages. PCBs designed using high-density interconnect techniques tend to be smaller as more components are packed in a smaller space. An HDI PCB uses blind, buried, and micro vias, vias in pads, and very thin traces to pack more components into a smaller area. We’ll show you the design basics for HDI and how Altium Designer® can help you create a powerful HDI PCB.

Test points in your electronic assembly will give you a location to access components and take important measurements to verify functionality. If you’ve never used a test point or you’re not sure if you need test points, keep reading to see what options you have for test point usage in your PCB layout.

The concept and implementation of differential impedance are both sometimes misunderstood. In addition, the design of a channel to reach a specific differential impedance is often done in a haphazard way. The very concept of differential impedance is something of a mathematical construct that doesn’t fully capture the behavior of each signal in a differential trace. Keep reading to see a bit more depth on how to design to a differential impedance spec and exactly what it means for your design.

Quite often, a standard assembly drawing is not enough to ensure the quality of a PCB assembly, especially when designing high-density boards. It would also be helpful to include additional detailing for simpler devices. The use of a Draftsman document brings an elegant, yet powerful solution to make these tasks easier.

An effective product lifecycle management (PLM) solution will integrate the tools and processes employed to design, develop and manufacture a new device. This solution goes beyond engineering activities to include the project management, process control, and financial management of the end-to-end business processes. PLM solutions create this collaborative environment where product development can flourish, bringing additional benefits in efficiencies and transparent communications, breaking silos, and speeding up the development process.

With ever increasing speeds in high-speed data systems comes a couple of PCB layout challenges. High-speed busses like DDR, VME, PCIe just to mention a few can all reach data transfer speeds that require strict timing with very tight tolerances, thereby leaving very little slack in the PCB layout. Watch this on-demand webinar to learn why it's imperative to match track lengths in high-speed data systems and differential signals. You’ll see how to properly define PCB length matching and time delay constraints, and how to effectively route high-speed signals in Altium Designer®.

In this article, we want to get closer to a realistic description of tight coupling vs. loose coupling in terms of differential pair spacing, as well as how the differential pair spacing affects things like impedance, differential-mode noise, reception of common-mode noise, and termination. As we’ll see, the focus on tight coupling has its merits, but it’s often cited as necessary for the wrong reasons.

You’ve possibly gone through plenty of engineering design reviews, both on the front-end of a project and the back-end before manufacturing. Engineering design reviews are performed to accomplish multiple objectives, and with many engineering teams taking a systems-based approach to design and production, electronics design teams will need to review much more than just a PCB layout and BOM. Today’s challenges with sourcing, manufacturability, reliability, and mechanical constraints are all areas that must be confronted in real designs

In this article, we’ll look at beamforming implementation in an advanced method combining analog and digital techniques, known as hybrid beamforming. This method blends both digital and analog techniques to create multiple beams and thus reach multiple users with varying intensities. In the case of an RF imaging system or a radar system, hybrid beamforming in a MIMO technique also allows tracking of multiple targets with adjustable resolution.

The problem with every via impedance calculator that I have seen is simple: they are incomplete or totally wrong. The “incomplete” part refers to a lack of context; these calculators can roughly reproduce a well-known estimate from a legend like Howard Johnson in his Digital Design textbooks. However, these calculators never provide insight into what they are actually calculating, or where the calculated via impedance is accurate. Keep reading to see why these calculators get it so wrong, as well as the context surrounding via impedance.

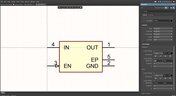

When designing high power circuits (usually very high voltage and/or current), you’ll need to create a regulator from scratch and place it in your PCB layout. It's also the case that you may want to model a real component using discretes in a simulation in order to qualify the system's expected operating regime. As part of buck converter design, you can easily run a buck converter simulation directly in Altium Designer’s schematic editor. Here’s how you can access these features in the newest version of Altium Designer.

Just as you get used to PCIe 5.0, they decide to release another standard! The newest iteration of PCIe is Gen6, or PCIe 6.0. PCIe 6.0 brings a doubling of channel bandwidth through introduction of PAM-4 as the signaling method in high-speed differential channels. This signaling method is a first for PCIe, and it’s an important enabler of the doubled data rate we see in the current standard. In this article, I’ll run over the important points in the standard and what PCB designers can expect when designing these channels.

One of the common implementations of SPI and I2C in a PCB layout is as a protocol for reading and writing to an external Flash memory. Flash chips are a very common component in embedded systems and can offer high capacities of non-volatile memory up to Gb values. When choosing a memory chip, you'll want to match the application requirements and functionality with the bus speed you need for read and write operations in your memory chip. There is also the matter of the type of Flash memory you'll need to access (NOR vs. NAND).

There is no SPI trace impedance requirement? The reality is that SPI lines only start to need impedance control when the length of the interconnect becomes very long. And because there is no specific impedance requirement in the bus, you have some freedom in channel design and termination. So what exactly qualifies as “very long” and when is some termination method needed? We’ll break it down in this article.

During this year's AltiumLive CONNECT event, I recall receiving an interesting question about the skin effect and the distribution of current due to the presence of ground in coplanar transmission lines. In this article, we'll look at the electric field around a transmission line carrying a signal, and how this might be impacted by the skin effect.

When you get your PCBA back from an assembler, you’ll notice the packaging materials used to pack and ship the PCBA. Those materials are specific to electronics, and if you build products on behalf of clients, it’s important to know the packaging materials used for packing and shipping electronics. In this article I’ll show the main set of materials and equipment used to package electronics assemblies.

Once you've got your PCB layout finished and you're ready to start preparing for manufacturing, one of the critical steps is to create PCB Gerber files. When you're ready to create your Gerber files, you need the right set of CAM processor tools that can take data from your PCB layout. In this article, we'll guide you through this process of how to make PCB Gerber files and show some example tasks you might need to perform to generate them.

One of the major factors impacting reliability of a PCBA is the use of teardrops on traces in the PCB. Like many aspects of reliability, the considerations also span into the signal integrity domain, particularly as more high-reliability products require greater data handling capabilities and run at higher speeds. In this article, I’ll break down the issues present in teardrop usage on differential pairs and how these may affect impedance.

High-reliability electronics must go through multiple rounds of testing and qualification to ensure they can withstand their intended operating environment. Designing to performance standards, whether the baseline IPC standards or more stringent industry standards, is the first step in ensuring a reliable circuit board. In this e-book, readers will gain a thorough look into PCB testing and analysis, starting from basic tests performed on bare boards and completed assemblies.

Coupling capacitors find plenty of uses in analog applications and on differential protocols, acting essentially as high pass filters that remove DC bias carried seen on a signal. In the case of PCIe, there are a few reasons to place AC coupling capacitors on differential pairs beyond the fact that AC coupling capacitors are listed in the standard. In this article, we’ll look briefly at where to place coupling capacitors on PCIe links, as well as the reasons these are placed on PCIe links.

We are happy to announce that the Altium Designer 22.7 update is now available. Altium Designer 22.7 continues to focus on improving the user experience, as well as performance and stability of the software, based on feedback from our users. Check out the key new features in the What's New section on the left side of this window!

Design to cost is a lofty idea that is only perfectly executed when supply and demand for components are in perfect harmony. Unfortunately, the current landscape for component sourcing makes design to cost more of a balancing act rather than an exercise in price reduction. To help designers in their efforts to balance cost, capabilities, and procurement, we created this ebook to help users understand how modern supply chain tools can help in these complex design problems.

Stubs are an important topic in high-speed PCB design, and there is a longstanding guideline that stubs should always be removed from all vias on high-speed digital interconnects. While stubs are bad for high-speed lines, they do not always need to be removed. What is more important is to predict the loss profile and frequencies, and to floorplan appropriately to try and prevent such losses.

Once you finish your placement and routing in your PCB layout, it can be tempting to wrap up the layout and send everything in directly to manufacturing. The reality is that the board may still need some work before it is considered finished. The cleanup you perform at the final stage of PCB layout will help you catch any outstanding errors that can't be programmed into your DRC engine, and it gives you a chance to add any outstanding details to the surface layers.