News & Updates

Even with all the good guidelines out there for high speed design, there are particular aspects of stackup construction and their relation to building boards that get overlooked. This blog is goes beyond just the typical SI/PI guidelines and looks at these problems from more of an engineering perspective.

Stitching vias are something you often see spread around the surface layer of a PCB, but what are they? and should you be using them? In this guide, we'll go over some of the standard uses of stitching vias and when they should be used in a PCB.

In comparison to the build-up of a PCB, the stackup is more concerned with the electrical type of each layer, that is are we working with signals, power, or ground. Continue reading to learn how you can optimize your layer stack.

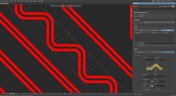

Altium’s VP of marketing Lawrence Romine discusses the multi-board and harness design capabilities coming in Altium Designer 23.

Controlled ESR capacitors are important for power integrity in your design as they can help smooth out the PDN impedance spectrum in your high speed PCB.

Whenever we say something to the effect of “components can’t work without a correctly designed PCB,” we only have to look at component packaging for evidence. It is true that component packages come with parasitics that affect signal integrity, but there is one area that we don’t often look at in terms of component packaging: power integrity.

Electronic components power nearly everything in our modern lives. However, as long as there are buyers for parts, counterfeiters will persist in their endeavors. Financial losses resulting from fake components are challenging to ascertain due to enforcement limitations and the difficulty in collecting data on the issue. In this article, we demonstrate how to test and verify components in batch orders.

With increased electronics supply chain visibility, you can develop better products faster and align perfectly with budget constraints early on. Here’s why.

Explore common myths about Agile hardware development and learn how to adapt Agile principles for hardware projects.

We are going deeper into lid assembly electronics in our Open Source Laptop project. In this chapter we will tackle the PCB design of the webcam board and show you how to deal with some expected challenges, such as overall small form factor of the board or breaking out the microscopic webcam image sensor.

If you're trying to understand how commercial Altium 365 differs from Altium 365 GovCloud, you're in the right place. Click to grasp the unique features of each.

Explore the challenges and strategies of implementing Agile methodology in electronics hardware development. Understand key differences between hardware and software development within the Agile framework.

The flexible circuits are ideal for applications where a thin, small, and lightweight PCB is needed. However, in such cases, challenges in assembly and fabrication often arise. This article delves into these challenges, focusing on component selection and placement and how they can significantly impact the performance of the flexible circuit in its intended application.

Have you ever performed manual tests? If your answer is yes, you're likely aware of how laborious and time-consuming the entire process can be. Allow us to introduce you to the realm of test equipment automation. Our new step-by-step guide empowers you to write code that seamlessly configures your networked test equipment, all from the convenience of your computer.

We are advancing with our brand new Pi.MX8 Project. In this chapter, we delve deeper into two crucial aspects: the overall schematic and component placement on the PCB board. Don't hesitate to check it out. Additionally, you can follow this project through our workspace; the link is provided within the article.

Dive into the world of High-Density Interconnect (HDI) design to enhance your projects. Explore heightened signal integrity, improved reliability, and the seamless integration of advanced technologies - all within compact and lightweight designs. Discover more about HDI on our updated feature page.

Ready to start collaborating on your OrCAD projects in a multi-CAD environment? Check how you can use Multi-CAD File Support in Altium 365 in practice.

A constraint-based approach to PCB design is crucial in today's electronics industry. This article delves deeper into this complex and interesting topic, exploring various types of constraints, their advantages, and providing guidance on implementing them into your PCB design process.

Do you have extensive knowledge about the Pi.MX8 module? We're excited to introduce a new series of articles focusing on an innovative approach to utilizing this module. In this inaugural chapter, we provide insights into the preparation for this project and detail the elements that will be used.

Learn why BOM management is critical for both procurement managers and electronic engineers. Altium 365 BOM Portal helps to bridge the gap between these worlds. Discover how!

Happy New Year! 🎉 We are thrilled to announce that the Altium 365 Assembly Assistant is now officially released and available for direct purchase through the Altium Store.

Creating documentation for hand PCB assembly does not prevent the same documentation from being utilized to assist in automated PCB assembly. Learn more about the optimal format for this data to enhance both your hand PCB assembly and overall assembly processes.